## A Practical Approach to Commercial Aircraft Data Buses

## **Revision History**

| Revision Date | Changes                            |

|---------------|------------------------------------|

| May, 2010     | Inital Release                     |

| June, 2010    | MIL-STD-1553 Goes Commercial Added |

| March, 2011   | TTP PHY Test Results Added         |

## SUMMARY OF PROPOSED SOLUTIONS

MIL-STD-1553 is a mature field proven technology that provides an ideal solution for emerging commercial aerospace applications. DDC is offering a wide variety of solutions based on this mature technology.

DDC is proposing:

- 1. MIL-STD-1553

- Existing 1 Mbps component solutions with 100 million flight hours of in service history available off the shelf today

- 2. TTP 1553

- > 4 Mbps technology demonstration board exists today

- Update existing transceiver component to support this higher speed and package with existing TTP controller into a single integrated multi-chip module

- 3. Turbo 1553

- Technology demonstrator with MIL-STD-1553 physical and protocol layers running at 3 to 5 Mbps in the lab today

- > Update existing transceiver and protocol components to support this higher speed

- 4. HyPer-1553

- Flight worthy technology demonstrator PMC supporting 40 to 200 Mbps exists today

- Size reduction and conversion of existing double wide PMC into a smaller form factor board product

## **Commercial Aerospace Data Bus Solutions**

## MIL-STD-1553

MIL-STD-1553 has been in use in flight and mission critical systems within military aircraft for over 30 years. The continued use of MIL-STD-1553 on new platforms such as F-22 and F-35 is a testament to the reliability of this interface. The current trend in commercial aircraft towards distributed processing architectures in real-time critical systems has created a need for a reliable, deterministic digital data bus. It is only natural that MIL-STD-1553 be considered as a leading candidate for these new commercial aircraft systems.

## TTP 1553 – SAE AS6003

Time Triggered Protocol (TTP) is an emerging data bus protocol that is finding its way into commercial aerospace applications. TTP is being released as an SAE Aerospace Standard (AS6003). RS-485 was initially the de facto physical layer for TTP however the performance of RS-485 has been found to be unacceptable for use in avionics applications. The proposed physical layer for AS6003 is MIL-STD-1553, as specified in AS6003 slash 1. DDC has developed a prototype 1553 physical layer interface that operates at 4 Mbps with commercially available TTP controller chips. This prototype physical layer card was used to refine the specifications for AS6003 slash 1.

## **TURBO-1553**

DDC has conducted research aimed at accelerating the speed of MIL-STD-1553 beyond its current 1 Mbps rate. The results of these tests showed that the data rate of MIL-STD-1553 can be reliably increased to 5 Mbps. DDC has developed prototype hardware that demonstrates the performance of a 5 Mbps "Turbo-1553" interface. Turbo-1553 provides an ideal solution for applications that demand the reliable deterministic performance of MIL-STD-1553 but need a slightly higher data rate. Turbo-1553 retains all the architectural benefits of MIL-STD-1553 while operating at a higher data rate.

## **HYPER-1553**

DDC has developed technology called HyPer-1553 that implements high speed digital data communication over legacy MIL-STD-1553 buses utilizing a broadband waveform such that this new high speed communication does not interfere with the legacy 1 Mbps 1553 communication while operating on the same bus. HyPer-1553 supports data rates from 40 to 100 Mbps for concurrent operation depending on bus length and number of nodes. Testing has also shown that data rates of 200 Mbps or higher are feasible on buses where legacy 1 Mbps MIL-STD-1553 communication is not present. HyPer-1553 can be used to implement a high speed multi-drop bus for use in commercial aircraft.

## TABLE OF CONTENTS

## Section 1: MIL-STD-1553 Goes Commercial

This paper explores some of the major attributes of MIL-STD-1553 and discusses why MIL-STD-1553 is an ideal choice for use in commercial aircraft systems.

## Section 2: MIL-STD-1553 Physical Layer for Time-Triggered Networks

Time Triggered networking technologies such as TTP (Time Triggered Protocol) are beginning to be used in critical aerospace applications such as flight controls. While TTP provides stringent specifications for determinism and fault tolerance, it does not define a physical layer. TTP's "de facto" physical layer, RS-485, includes shortcomings in a number of areas. The first white paper in this section presents the benefits of Mil-STD-1553 over RS-485 as a physical layer for TTP. A second white paper presents the test results of a technology demonstration of 1553 as a physical layer for TTP.

## Section 3: 1553 Evolution White Paper

MIL-STD-1553 combines a robust physical layer with a deterministic protocol making it ideally suited for use in commercial aerospace systems. While MIL-STD-1553's 1 megabit-per-second data rate is still adequate for a large number of applications, there are systems that require higher rates. This white paper discusses two approaches for increasing the bandwidth of MIL-STD-1553 that are gaining momentum.

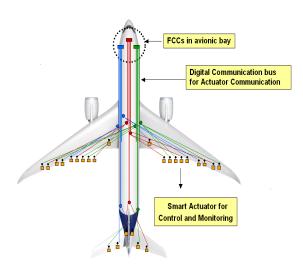

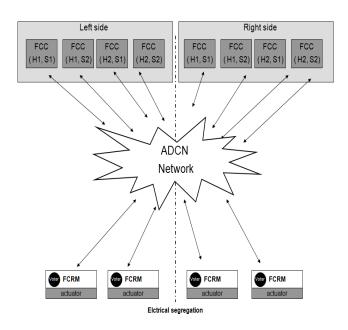

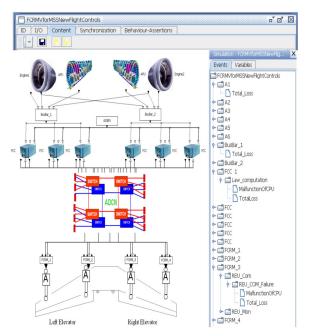

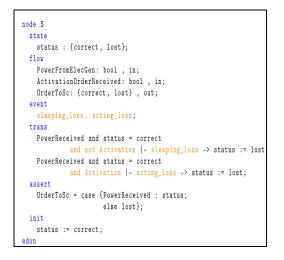

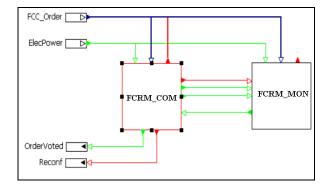

## Section 4: Distributed and Reconfigurable Architecture for Flight Control System

This white paper discusses some evolutions for Flight Control System (FCS) and how to build alternative FCS using low-cost and safe architectures with less hardware and software resources. The paper presents a full distributed reconfigurable architecture for FCS based on smart actuators and digital communication network where all system functions are distributed to simplex Flight Control Computer (FCC) nodes and remote actuator electronics nodes (FCRM) with communication between FCC and FCRM based on a MIL-STD-1553 bus.

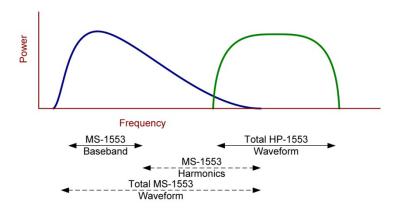

## Section 5: High Performance 1553

This white paper provides a summary of DDC's initial study into the feasibility of running higher speed over legacy MIL-STD-1553 data buses. The results of DDC's analysis is that for some MIL-STD-1553 buses there is sufficient bandwidth to implement a broadband system in which legacy 1 Mbps 1553B waveforms could coexist with new 200 Mbps waveforms, thus providing for an increment high speed communication channel to existing MIL-STD-1553 buses.

## Section 6: DDC's A350 Press Release

This press release describes Airbus's selection of DDC's MIL-STD-1553 component for use in the primary flight control system on the A350 XWB.

## **SECTION 1:**

## **MIL-STD-1553 GOES COMMERCIAL**

## MIL-STD-1553 Goes Commercial

## Introduction

MIL-STD-1553 is a serial data bus that has been used as the primary command and control interconnect in military aircraft for the past three decades. MIL-STD-1553's robust performance, high level of interoperability, large installed based, and well established infrastructure of vendors has made MIL-STD-1553 the network of choice for military avionics systems around the world.

The use of MIL-STD-1553 is not limited to military aircraft. MIL-STD-1553's use is pervasive in military ground vehicles, military ships, UAVs, missiles, and satellite systems. More recently MIL-STD-1553 has been selected for use in the primary flight control system for a commercial aircraft(1). All of these applications share common requirements for a reliable, fault tolerant data bus that will operate in relatively harsh environments. Aircraft applications have unique environmental requirements such as lightning immunity, wide temperature range, high vibration, and high electromagnetic interference (from sources such as radar). MIL-STD-1553 was explicitly designed to operate in these demanding environments.

This paper explores some of the major attributes of MIL-STD-1553 and discusses why MIL-STD-1553 is an ideal choice for use in commercial aircraft systems.

## **Physical Layer**

One of the key architectural features of MIL-STD-1553 is the use of transformers. Transformers are used for two fundamental purposes: galvanic isolation and impedance matching. Galvanic isolation is a major benefit in systems, such as aircraft, that have severe EMI and lightning requirements. Isolation is even more critical in new composite aircraft where the skin of the aircraft no long provides an inherent Faraday shield as was the case with aluminum skinned aircraft.

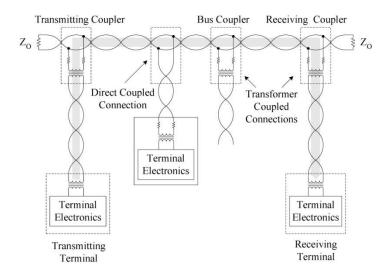

MIL-STD-1553 defines the topology to be a multi-drop linear bus. Multi-drop buses tend to be lower cost, lower complexity, and lower weight than a switched fabric network. The challenge in implementing a multi-drop bus is to maintain signal integrity to all the receivers on the bus. One of the biggest impediments in a multi-drop bus is reflections. MIL-STD-1553's use of bus couplers is a unique architectural feature that reduces reflections and thus contributes to the performance of this robust physical layer.

### **Minimizing Reflections**

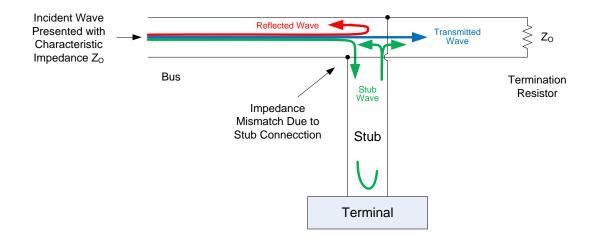

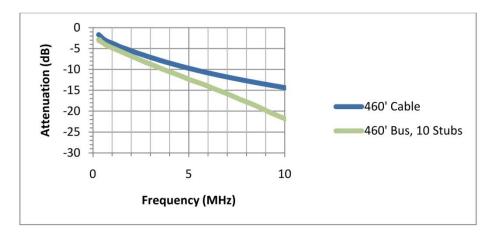

A multi-drop bus starts with a main bus cable that has a characteristic impedance of  $Z_0$  and is terminated into a resistive load equal to  $Z_0$ . Transmissions will propagate down the bus and will be dissipated into the termination resistor. Stub cables are then used to connect terminals (communication end points) to the bus. Reflections will occur due to the mismatch in impedance on the main bus caused by the stub connection (refer to Figure 1). Part of the incident wave will be reflected (reflected wave), part will be transmitted up the stub cable (stub wave), and a portion will continue down the transmission line (transmitted wave).

Figure 1. Reflections Caused by Impedance Mismatch

It may be expected that a stub cable be terminated with the characteristic impedance at the terminal interface, however, MIL-STD-1553 defines that the terminal must have a relatively high input impedance. The high input impedance of the terminal relative to the characteristic impedance will produce a large reflection coefficient at the terminal connection to the stub. The result of this high impedance is that most of the stub wave will be reflected back toward the bus and will add back into the incident wave with a phase shift due to the delay down the stub and back. If the terminal were terminated in the characteristic impedance then the signal would be attenuated at every stub connection, and would significantly limit the number of terminals that could be connected to the bus. Instead 1553 minimizes the attenuation due to the stub at the expense of a slight amount of phase distortion.

The amount of reflection on the main bus will be based on the impedance mismatch caused by the stub (refer to Equation 1). The impedance at the stub connection  $(Z_L)$  will be a result of the cable's characteristic impedance in parallel with the impedance of the stub. A higher stub impedance will produce a higher  $Z_L$  and result in a lower reflection coefficient ( $C_R$ ).

Equation 1. Reflection Coefficient

$$C_R = \frac{Z_L - Z_0}{Z_L + Z_0}$$

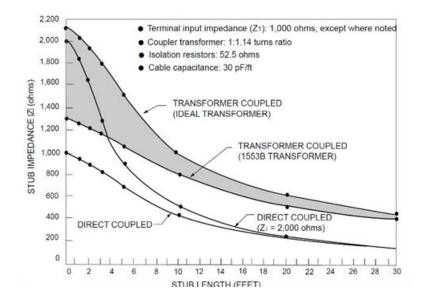

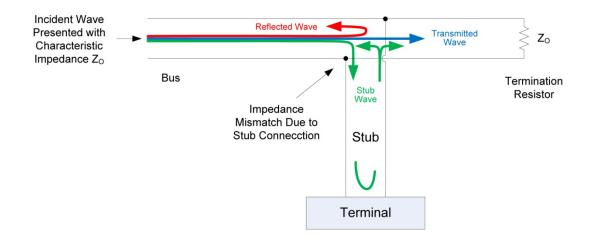

Increasing the impedance of the stub will reduce the amount of reflections on the main bus. The impedance of the stub will be based on the combination of the input impedance of the terminal and the distributed impedance of the cable. Figure 2 illustrates the first –order magnitude calculation of the impedance of the stub as a function of stub length. The figure shows that a 20 foot direct coupled stub with a terminal input impedance of 2000 ohms will result in a stub impedance of less than 300 ohms.

Figure 2. Stub Impedance Versus Stub Length

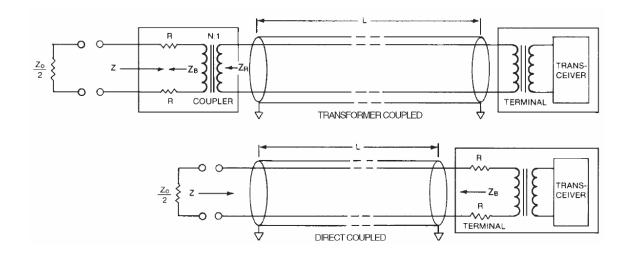

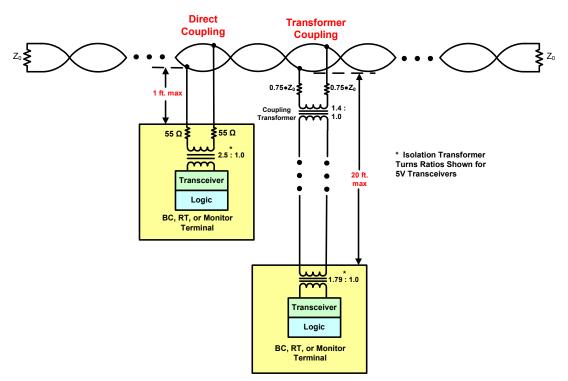

MIL-STD-1553 defines the option for a transformer coupled connection which utilizes a bus coupler to increase the input impedance of the stub and thus reduce reflections on the main bus. The bus coupler contains a transformer with a turns ratio of 1:1.41 (refer to Figure 3). The transformer will increase the effective impedance of the stub by the turns ratio squared (i.e. by a factor of 2 to 1).

Referring to Figure 2, a transformer coupled terminal will have an input impedance of 1000 ohms. With a stub length of zero the impedance of the terminal will be increased by factor of two (plus the 52.5 ohm series resistors), resulting in an effective stub impedance of 2105 ohms (assuming an ideal transformer). Figure 2 also illustrates the more realistic case using an actual transformer, which will provide an effective stub impedance of approximately 1300 ohms for zero stub length. The real benefit of the transformer coupled connection can be seen with longer stubs lengths. The impedance of a 20 foot stub using transformer coupling will be almost twice the impedance of a direct coupled stub.

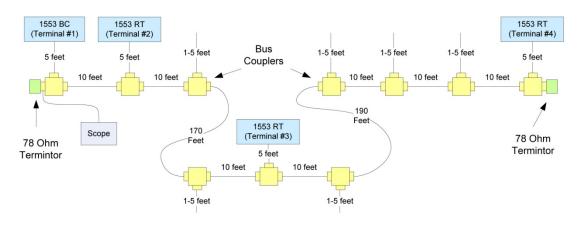

#### Figure 3. Bus Topology

MIL-STD-1553's transformer coupled connections enable the use of relatively long stubs (up to 20 feet or longer) while still maintaining reasonable transmission line characteristics on the main bus (i.e. minimizing reflections and attenuation).

### **Fault Isolation**

MIL-STD-1553 provides the benefit of fault isolation through the use of series resistors in the path between stubs and the main bus. The fault isolation resistors will allow the network to continue operating even in the presence of a short circuit on one of the stub connections.

### **Impedance Matching**

The values of the isolation resistors and the turns ratio of the coupling transformers are specified such that a matched impedance is presented on the stub input to a bus coupler which helps reduce signal distortion due to secondary reflections on the stub. Refer to Figure 4. A direct coupled terminal will be presented with a bus impedance  $Z_B$  which is equal to  $Z_0/2$  at the end of the stub. A transformer coupled terminal will be presented with a reflected impedance  $Z_R$  through the coupling transformer. The bus impedance for the transformer coupled configuration consists of  $Z_0/2$  (termination resistors) in series with two isolation resistors with a value of  $0.75 * Z_0$ . Therefore the bus impedance  $Z_B$  for a transformer coupled terminal will be  $Z_0/2 + 2 * 0.75 * Z_0 = 2 * Z_0$ . The impedance reflected through the transformer ( $Z_R$ ) will be increased by the turns ratio squared.  $ZR = Z_B/(1.41)^2 = Z_0$ . The net effect of the bus coupler is that the impedance from the stub looking into the bus coupler is equal to the characteristic impedance  $Z_0$  which means that the stub is presented with a matched impedance, which will reduce reflections on the stub.

#### Figure 4. Transformer and Direct Coupled Stubs

MIL-STD-1553 combines stringent transmitter and receiver specifications with a generous link budget to produce a robust data bus that is extremely tolerant to various channel conditions based on bus length, number of nodes, and environmental conditions (such as noise, EMI, and lightning).

## **Protocol Layer**

MIL-STD-1553's use of a command/response protocol enables highly deterministic communication making it ideal for real-time command and control functions, which typically require the transfer of data at a periodic rate (isochronous communication). Every transfer on the bus is initiated by a central bus controller (BC). The centralized bus controller allows the scheduling of data transfers with microsecond accuracy and very low jitter.

### **Reliable Link Layer**

MIL-STD-1553 combines error detection with acknowledgement to implement a reliable link layer protocol. All data transfers on the 1553 bus start with a command word from the BC and include a status response (acknowledgement) from a Remote Terminal (RT). The RT is required to respond to the command within 12 usec. The BC will wait a minimum of 14 usec for the RT response before considering the message to have timed out. Following a timeout the BC has the option of retrying the message either on the same bus or on the redundant bus. 1553's short response timeout value (14 usec) and relatively small payload size (64 bytes max) allow for efficient retransmissions. 1553 also includes support for dual redundancy making it an ideal choice for high availability systems.

### **Time Synchronization**

Many distributed processing systems require time synchronization. MIL-STD-1553 provides the facility for a Remote Terminal to synchronize their local time through the use of the "synchronize" and "synchronize with data" mode codes (protocol specific messages). The synchronize mode code is generally used to reset a local free running counter within the MIL-STD-1553 controller chip while the synchronize with data mode code is used to load the local free running counter within MIL-STD1553 controller chips, such as DDC's ACE series of components, implement the synchronize mode codes autonomously (without host processor intervention) which enables accurate distribution of time with minimal impact on processor bandwidth. The synchronize mode codes facilitate time partitioning and just in time delivery of data.

### Test Plans (Certifiability / In-service History / Maturity

One of the hallmarks of MIL-STD-1553's success over the years has been the high level of interoperability between MIL-STD-1553 interfaces in different boxes. Interoperability is a fundamental requirement for integration of complex systems. Compliance to MIL-STD-1553 is ensured through a suite of validation and production test plans (refer to Table 1). These test plans are published by the Society of Automotive Engineers as Aerospace Standards.

| Table 1. Summary of MIL-STD-1553 Compliance Test Plans |                                                                                                                 |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|

| AS4111                                                 | Validation Test Plan for Aircraft Internal Time Division<br>Command/Response Multiple Data Bus Remote Terminals |  |

| AS4112                                                 | Production Test Plan for Aircraft Internal Time Division<br>Command/Response Multiple Data Bus Remote Terminals |  |

| Table 1. Summary of MIL-STD-1553 Compliance Test Plans |                                                                                                                |  |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|

| AS4113                                                 | Validation Test Plan for Aircraft Internal Time Division<br>Command/Response Multiple Data Bus Bus Controllers |  |

| AS4114                                                 | Production Test Plan for Aircraft Internal Time Division<br>Command/Response Multiple Data Bus Bus Controllers |  |

| AS4115                                                 | Test Plan for the Digital Internal Time Division Command/Response<br>Multiplex Data Bus System                 |  |

In addition to a rigorous suite of compliance test plans MIL-STD-1553 also has millions of flight hours of in-service history to attest to its reliable operation in an aircraft environment. DDC has estimated that one of their MIL-STD-1553 controller chips has over 65 million flight hours of in-service history. Validation testing and inservice history are important contributors to the design assurance level of systems, especially aircraft systems that will ultimately need to meet the requirements of DO-178 and DO-154.

## Conclusion

Why consider a new, unproven technology for use in a flight environment when a mature technology like MIL-STD-1553 is available? The reliability and robustness of MIL-STD-1553 has been proven based on decades of flight history. In addition, MIL-STD-1553 is more cost effective than most people realize. A common misconception is that a 1553 interface is very expensive when in reality the cost of a MIL-STD-1553 node has consistently decreased in price over the last 10 years. MIL-STD-1553 is a natural choice for use in commercial aircraft systems.

#### **Michael Hegarty**

Principal Marketing Engineer Data Device Corporation

For more information, contact Michael Hegarty at 631-567-5600 ext. 7257 or Hegarty@ddc-web.com. Visit DDC on the web: www.ddc-web.com.

Data Device Corporation is recognized as an international leading supplier of high-reliability data interface products for military and commercial aerospace applications since 1964 and MIL-STD-1553 products for more than 25 years. DDC's design and manufacturing facility is located in Bohemia, N.Y.

## References

1. **Data Device Corporation**. 2010 Press Releases. *Data Device Corporation Web Site*. [Online] Data Device Corporation, March 2, 2010. [Cited: March 10, 2010.] http://www.ddc-web.com/News/Press/DDC\_Airbus.aspx.

## **SECTION 2:**

## MIL-STD-1553 PHYSICAL LAYER FOR TIME-TRIGGERED NETWORKS

#### 09ATC-0129

### MIL-STD-1553 Physical Layer for Time-Triggered Networks

Mike Glass

Data Device Corporation

Copyright © 2009 SAE International

#### ABSTRACT

Time Triggered networking technologies such as TTP (Time Triggered Protocol) are beginning to be used in critical aerospace applications such as flight controls. While TTP provides stringent specifications for determinism and fault tolerance, it does not define a physical layer. TTP's "de facto" RS-485, physical layer, includes shortcomings in a number of areas. These include a relatively low minimum transmitter voltage, low receiver threshold, along with a lack of specificity in a number of areas. The latter include bus signal levels, transmitter zero-crossing distortion and receiver zerocrossing tolerance. isolation method. terminal output noise, common mode and noise rejection, and input impedance. MIL-STD-1553, which has been deployed in flight and mission critical military applications for decades, defines a highly proven and robust physical layer. This paper presents MIL-STD-1553's physical layer as a candidate for use with TTP.

#### INTRODUCTION

Physical layers represent important components for buses and networks used in flight critical applications, with tradeoffs involving topology, data rate, cable length, power, and cost. Time triggered technologies such as TTP (Time Triggered Protocol) and FlexRay use multiple topologies, including multi-drop buses, along with active and passive stars. TTP does not specify a physical layer, resulting in the deployment of multiple implementations rather than use of a common standard.

MIL-STD-1553's multi-drop bus physical layer operates in demanding applications such as flight control, mission computers, and weapons for fighter and attack aircraft. The maturity and technical characteristics of MIL-STD-1553's physical layer make it a strong candidate for use with time triggered networks.

MIL-STD-1553 defines a highly robust and proven physical layer. For use with time triggered technologies, 1553's 1 Mb/s data rate can be scaled to operate at 5 or 10 Mb/s by means of upgraded transceiver and transformer design, and use of 8B/10B encoding.

MIL-STD-1553's physical layer offers many advantages for time triggered networks. These include differential signaling, with a defined "idle" state to help prevent collisions between consecutive transmitters. MIL-STD-1553's use of transformer isolation and optional transformer bus coupling provide DC isolation, common mode rejection, and lightning protection, with series isolation resistors to protect against short circuit faults. The transformer bus coupling option increases stub impedance to enable increased stub lengths.

MIL-STD-1553's relatively high transmit voltages provide strong data rate/cable 1553's performance. while length specifications for rise and fall times limit EMI emissions. Additional 1553 specs include transmitter zero-crossing distortion. overshoot, ringing, droop, output noise, and output symmetry. MIL-STD-1553's output symmetry spec limits the amplitude and duration of "tails" at the end of a node's transmission.

MIL-STD-1553 also defines specs for "must ignore" and "must recognize" receiver voltages, plus requirements for zerocrossing distortion, common mode rejection, noise rejection, and terminal input impedance. MIL-STD-1553B also specifies voltage ranges delivered by the bus cable to all receiving nodes on the bus. The affect of these latter specs is to impose a maximum loss budget on the bus.

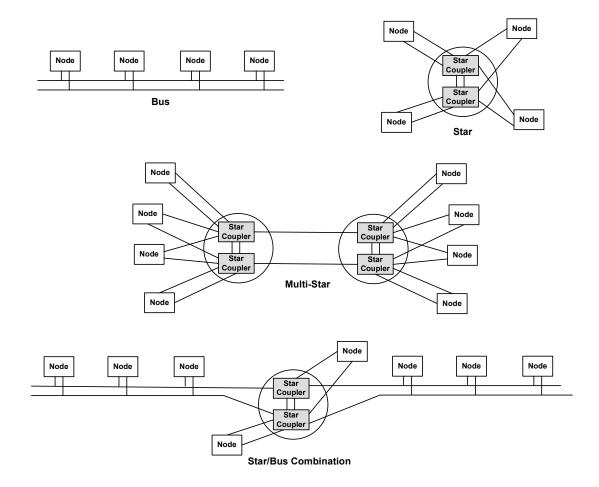

## TTP and FLEXRAY -- PHYSICAL LAYERS

Time triggered networks such as TTP (Time Triggered Protocol) and FlexRay deploy multiple topologies. As shown in Figure 1, these include multi-drop bus, active star, passive star, and combinations thereof. Active stars entail penalties in the areas of component volume and weight, cable volume and weight, power, and cost. In these respects, the use of a multi-drop passive bus offers advantages over an active star.

TTP does not define a standard physical layer. This has led to the deployment of multiple physical layers for different implementations, rather than the adoption of a common standard. TTP's "de facto" physical laver. RS-485. includes shortcomings in a number of areas. These include relatively low values for required transmitter voltage and receiver threshold, along with a lack of specificity in a number of specs. The latter include transmitter and receiver zero-crossing distortion, isolation method, bus signal levels, terminal output noise, common mode and noise rejection, and input impedance.

For many decades, MIL-STD-1553 has provided proven and reliable operation in demanding applications such as flight control, mission computers, and weapons control for fighter, attack, and transport aircraft. MIL-STD-1553's maturity and technical characteristics make it a strong candidate as a physical layer for time triggered protocols such as TTP and FlexRay.

MIL-STD-1553 is defined for a 1 Mb signaling rate using Manchester encoding, and therefore a 1 Mb/s data rate. For use

with time triggered technologies, 1553's physical layer specifications can be scaled for operation at signaling rates of 5 or 10 Mb.

A basic issue with a multi-drop topology involves the tradeoff between data rate and cable length. This involves loss budget, cable attenuation, stub and node impedances, the number of stubs, and stub lengths. To ensure low bit error rates, multidrop buses must be defined to provide adequate levels of signal integrity to all receiving nodes.

MIL-STD-1553 defines differential signaling, with three voltage states: idle, active high, and active low. For use with time triggered technologies, the inclusion of an idle voltage level enables receivers to more easily determine "dead time", thereby indicating to the next node to transmit that the bus is "safe"; i.e., there won't be a collision with the preceding node's transmission. Further, the use of a differential, rather than singleended bus provides advantages in the areas of common mode performance EMI, and lightning immunity. To preclude the possibility of a short circuit fault "taking down" an entire bus, MIL-STD-1553 includes a requirement for all nodes to include series isolation resistors.

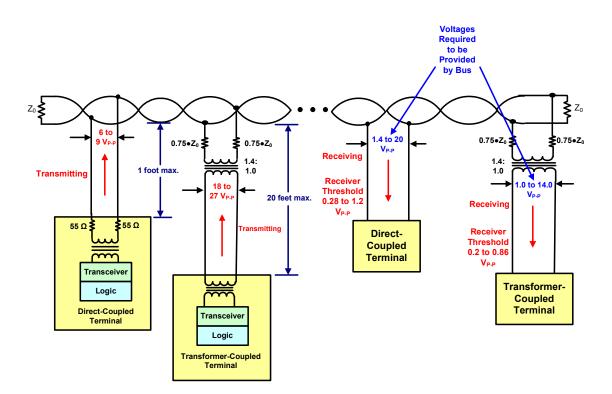

#### DIRECT and TRANSFORMER COUPLING

As shown in Figure 2, MIL-STD-1553 provides two different configurations for coupling a node to a 1553 bus, direct coupling and transformer coupling. It is possible to include a mix of the two types of coupling methods on the same data bus.

MIL-STD-1553 requires the use of transformer isolation for both direct-coupled and transformer-coupled terminals. This provides robustness in the areas of DC isolation, survivability for lightning, and common mode rejection.

Figure 1. TTP Topologies: Bus, Star, Multi-Star, and Star/Bus Combination<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Time-Triggered Protocol TTP/C High-Level Specification Document Protocol Version 1.1, page 21.

Direct coupling includes a requirement for 55 ohm isolation resistors in series with each leg of the isolation transformer. This provides protection in the case of a short circuit in a terminal's transformer or transceiver. If a short circuit occurs, the terminal will load the data bus with 110 ohms, rather than a dead short, allowing the remaining terminals on the bus to continue operation despite the fault. With direct coupling. the recommended maximum distance between the terminal and its connection to the data bus is one foot. The short stub length minimizes the possibility of a short circuit in the sub wiring, which is unprotected by the isolation resistors. In addition, this limitation also minimizes the loading of the data bus from the stub cable's capacitance.

Figure 2 also illustrates MIL-STD-1553 transformer coupling. Transformer coupling entails the use of a bus coupler to interface a terminal's stub to the data bus. As shown, the bus coupler consists of a coupling transformers and a pair of bus isolation resistors. Unlike for direct coupling, there are no isolation resistors in a transformercoupled terminal. The value of these resistors is 0.75•Z<sub>0</sub>. These resistors provide protection against short circuit faults in the transformer. stub. coupling and the terminal's isolation transformer and transceiver.

Figure 2. 1553 Direct and Transformer Coupling

MIL-STD-1553 specifies parameters for the coupling transformers, including:

- Turns ratio: 1.4 to 1.0, stepping down, from the bus to the stub.

- Open circuit impedance (on the bus side): ≥ 3,000 ohms, over 75 KHz to 1 MHz.

- Droop: ≤ 20%

- Ringing: ≤ 1 V<sub>pk</sub>.

• Common mode rejection ratio:  $\geq$  45 db.

For transformer-coupled terminals, MIL-STD-1553 recommends a maximum distance between the bus and the terminal of 20 feet. Since stub impedance decreases as a function of stub length, the purpose of this recommendation is to limit the bus loading created by individual stubs. Excessive stub loading increases transmission line reflections, resulting in waveform phase distortion. In addition, increased stub loading tends to reduce the bus voltage.

Transformer coupling enables longer stubs by doubling the stub impedance as "seen" by the main bus cable. In addition, it provides impedance matching for transmitters (the load on the transmitter =  $Z_0$ ). Further, relative to direct coupling, transformer coupling provides improvements in DC and ground isolation, lightning protection, and common mode rejection.

## DATA ENCODING and WAVESHAPING

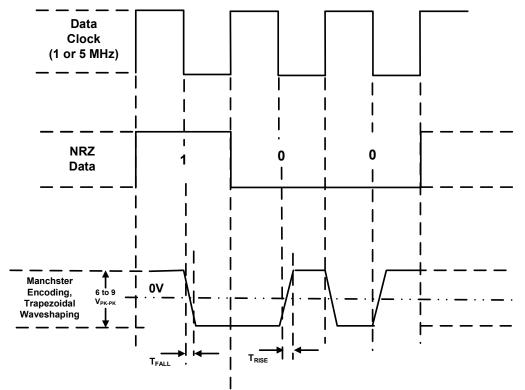

Figure 3 and Figure 4 illustrate MIL-STD-1553's basic data encoding and waveshaping specifications. As shown in Figure 3, the encoding method specified by MIL-STD-1553 is Manchester II. or Manchester Biphase-L. For a 1 Mb/s data rate, Manchester encodes a logic '1' as a 500 nS positive voltage, followed by a 500 nS negative voltage; and a logic '0' as a 500 nS negative voltage, followed by a 500 nS positive voltage. In addition to its simplicity, another advantage of Manchester encoding is its transition density. Since Manchester provides a minimum of one signal transition per bit time, this helps to facilitate reliable clock recovery, and the use of oversampling decoding techniques. Further, Manchester encoding provides a balanced waveform with zero DC component, thereby enabling transformer isolation.

Figure 3. MIL-STD-1553 Encoding and Waveshaping

The 6 to 9 volt peak-to-peak signal amplitude spec shown in Figure 3 refers to the transmitter output for direct coupled terminals. For stub coupled terminals, MIL-STD-1553 specifies 18 to 27 volts across

the transmitter stub driving a 70 ohm load. This results in approximately 6.36 to 9.54 volts peak-to-peak driven on to the bus. As shown in Figure 3 and Figure 4, 1553 specifies trapezoidal waveshaping with a range of rise and fall times of 100 to 300 ns. These times are defined as the transition times between the 10% and 90% points of the peak-to-peak voltage. Trapezoidal, rather than sinusoidal waveshaping, results in simpler transmitter designs, including improved control over the important parameter of zero crossover timing.

The purpose of the lower limit on rise/fall times is to limit the harmonic content of the signal above 1MHz. This serves to minimize EMI and crosstalk, as well as transmission line reflections that can result in false zero crossings and possible decoding errors. Most transmitter designs tend toward the lower limit of the rise/fall time standard as a means of minimizing drive stage power dissipation.

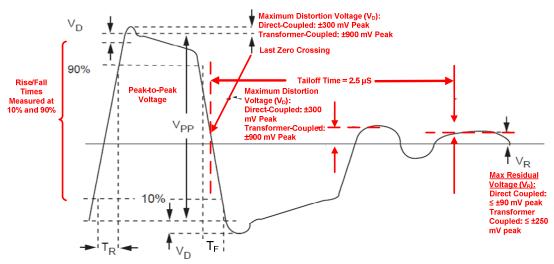

As shown in Figure 4, MIL-STD-1553 limits the overshoot and ringing distortion of the differential transmitted voltage to less than  $\pm 300.0$  mV peak for direct-coupling, and less than  $\pm 900.0$  mV peak for transformer coupling. As shown, this spec is applicable for all rise and fall transitions during a transmission, as well following the end the last Manchester half-bit transmitted.

MIL-STD-1553 includes an additional limit on the distortion at the end of a node's transmission. This spec, commonly referred to as "output symmetry" or "dynamic offset", provides a limit on the residual voltage or "tail". Specifically, this limits the voltage 2.5  $\mu$ S after the mid-bit zero crossing of the last transmitted bit to less than ±90 mV for a direct-coupled transmitter, or less than ±250 mV for a transformer-coupled transmitter.

For a time-triggered network, this residual voltage spec helps to ensure a "dead bus" following one node's transmission prior to the start of transmission by the subsequent node. A related spec in this respect is that for maximum output noise from a non-transmitting terminal. MIL-STD-1553 limits

this to less than 5 mV RMS for a directcoupled terminal, or less than 14 mV RMS for a transformer-coupled terminal.

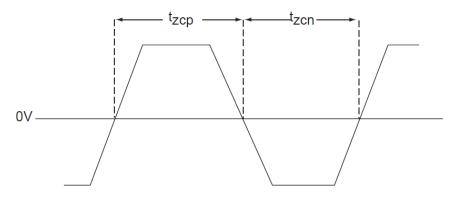

#### ZERO-CROSSING DISTORTION

Figure 5 illustrates another transmitter parameter, zero-crossing distortion. In other networking standards, this is referred to as jitter. Zero-crossing distortion has to do with the time between zero crossings of a Manchester encoded transmitted signal. The times  $t_{zcp}$  and  $t_{zcn}$  in Figure 5 represent the respective pulse widths of the positive and negative voltage pulses. For MIL-STD-1553 1 Mb/s Manchester encoded signals, the nominal times for  $t_{zcp}$  and  $t_{zcn}$  are 500 and 1000 nS. Per MIL-STD-1553, the maximum

deviation from these nominal times is  $\pm 25$  nS; that is, 500  $\pm 25$  nS, or 1000  $\pm 25$  nS.

In addition to specifying maximum zerocrossing distortion on the transmitting side, 1553 also specifies a minimum tolerance for receivers' zero-crossing distortion tolerance. For  $t_{zcp}$  and  $t_{zcn}$ , the minimum value of this parameter is ±150 nS. That is, a receiving terminal must accept as valid input signals with zero-crossing distortion of up to  $\pm 150$ nS. This, together with the  $\pm 25$  nS tolerance on the transmit side, allows a "zero-crossing distortion budget" of up to  $\pm 125$  nS that can be introduced as the result of transmission line reflections from stubs, and from the bus cable.

Figure 5. Zero-Crossing Distortion

## DATA BUS and RECEIVER VOLTAGES

While MIL-STD-1553A specified a maximum length of 300 feet for the main bus cable, MIL-STD-1553B eliminated this restriction. In its place, as shown in Figure 6, 1553B specifies minimum and maximum voltages that a bus must deliver to all stubs. As shown, a MIL-STD-1553B bus must deliver 1.4 to 20 volts peak-to-peak to all directcoupled stubs, and 1.0 to 14 volts peak-topeak to all transformer-coupled stubs. This, in effect, mandates a maximum loss budget for the bus of slightly over 12.6 dB.

MIL-STD-1553B receiver voltage specs are based on the concept of a threshold; that is, the voltage above which a node must consider a received 1553 message to be valid. For direct-coupled terminals, the maximum threshold is 1.2 V peak-to-peak, while for transformer-coupled terminals, the maximum threshold is 860 mV. Relative to the minimum voltage level that must be provided by the bus, this provides a minimum margin of 200 mV peak-to-peak for direct-coupled terminals, and 140 mV for transformer-coupled terminals.

In addition to the maximum threshold voltage, 1553B also specifies minimum "no

respond" voltages. That is, received signal levels below this value must not be considered to be valid. For direct-coupled terminals, the minimum "no respond" voltage 280 mV peak-to-peak, while is for transformer-coupled terminals, the "no respond" voltage is 200 mV. These "no respond" voltages specify a definitive "dead zone", allowing a node to determine that no other nodes are transmitting. In addition, they provide an inherent degree of noise immunity.

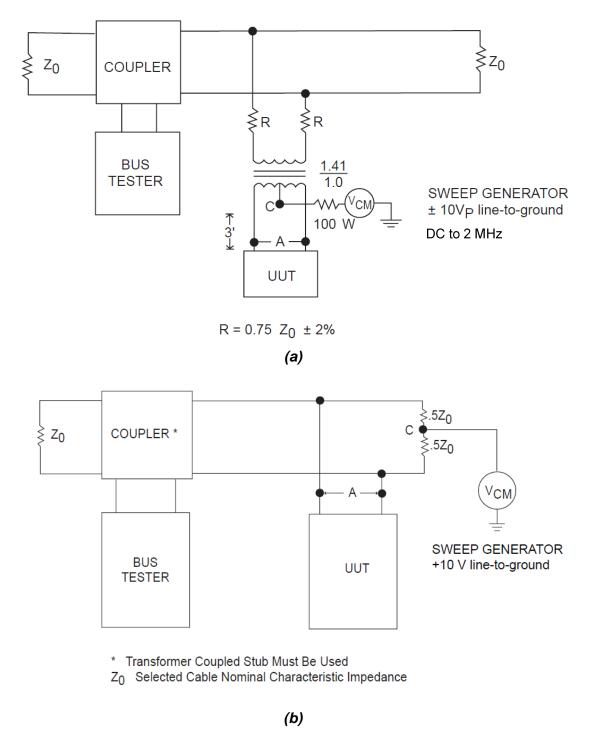

#### **COMMON MODE REJECTION**

MIL-STD-1553 specifies a minimum level of common mode rejection for all terminals. Common mode rejection is partially a characteristic of the terminals' isolation transformers, and is a form of noise disturbance commonly encountered in avionics.

As shown in Figure 7(a), for the common mode test for a transformer-coupled terminal, the common mode signal is applied between the center tap of the bus coupling transformer on the "stub" side and ground. As shown in Figure 7(b), for a direct-coupled terminal, the common mode signal is applied between the junction of two "halftermination" resistors  $(0.5 \bullet Z_0 \text{ each})$  and ground.

For the terminal common mode rejection test, the minimum signal level of 860 mV peak-to-peak transformer-coupled, or 1.2 V

direct-coupled is used. The common mode signal applied includes  $\pm 10$  VDC, and a  $\pm 10$  V (peak) AC voltages whose frequency is swept from 1 Hz to 2 MHz. To pass, the terminal must accept all messages received.

Figure 6. MIL-STD-1553 Bus, Stub, and Receiver Voltages

#### **INPUT IMPEDANCE**

Another 1553 physical layer spec is terminal input impedance. The importance of input impedance is that it effects the loading on the main bus. Excessive stub loading increases transmission line reflections, resulting in waveform phase distortion, and tends to reduce the bus voltage. MIL-STD-1553 specifies a minimum terminal input impedance over the frequency range of 75 KHz to 1 MHz. This represents the range of fundamental frequencies for 1553 signals.

For direct-coupled terminals, the terminal input impedance must be a minimum of 2,000 ohms, while for transformer-coupled terminals, the terminal input impedance must be a minimum of 1,000 ohms. The reflected impedance of transformer-coupled terminals to the main bus is doubled by the 1.4 to 1.0 turns ratio of the bus coupling transformer.

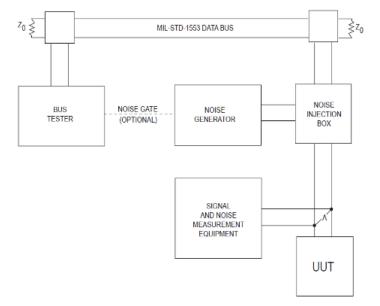

#### NOISE REJECTION (BIT ERROR RATE)

Another spec for 1553 terminals is noise rejection, or bit error rate testing. MIL-STD-1553B defines a test for terminals to be able to receive messages in the presence of white, Gaussian noise applied differentially across the data bus or stub. This test, which is defined within the 1553 standard, provides a figure-of-merit test criteria for operating in an environment including switching power supplies, radios, radar, electromechanical switching, and other sources of EMI.

<sup>&</sup>lt;sup>2</sup> SAE AS4111; Validation Test Plan for the Digital Time Division Command/Response Multiplex Data Bus Remote Terminals; Figure 6A, page 60; and Figure 6B, page 61.

Figure 8. Noise Rejection (Bit Error Rate) Test

The 1553 noise test specifies signal and noise levels, with a signal-to-noise ratio of approximately 16.6 dB. For direct-coupled terminals, the test entails the use of a signal level of 3.0 volts peak-to-peak and a white Gaussian noise source of 200 mV RMS distributed over 1.0 to 4.0 MHz. For transformer-coupled terminals, the test specifies a signal level of 2.1 volts peak-to-peak and a white Gaussian noise source of 140 mV RMS.

In both cases, the terminal must demonstrate a word error rate of less than  $10^{-7}$ , equivalent to a bit error rate of  $2 \bullet 10^{-9}$ .

#### **BUS ISOLTION**

To ensure independence for redundant buses, MIL-STD-1553 specifies a minimum isolation of 45 dB between buses.

#### VALIDATION TESTING

One of the keys to MIL-STD-1553's longterm success in military use is its defined and publically available criteria for validation testing. This delineates a rigorous suite of tests, to which a terminal must demonstrate compliance to. This test includes all of the physical layer parameters discussed in this paper, along with comprehensive protocol testing. As a result, while MIL-STD-1553 has been implemented by many dozens of different designers over the years, it has historically *not* encountered issues with interoperability.

#### CABLE

MIL-STD-1553's cable specifications include the use of twisted/shielded cable, with a defined characteristic impedance, maximum attenuation, shielding coverage, capacitance, twists per foot, and EMC. Table 1 lists MIL-STD-1553's cable characteristics.

#### Table 1. MIL-STD-1553 Cable Characteristics

| Property | Value |

|----------|-------|

|          |       |

| Туре                                       | Twisted-shielded pair             |

|--------------------------------------------|-----------------------------------|

| Characteristic impedance (Z <sub>0</sub> ) | 70 to 85 ohms at 1.0 MHz          |

| Attenuation                                | 1.5 dB/100 ft at 1.0 MHz, maximum |

| Shielding Coverage                         | 75% minimum                       |

| Length of main bus                         | Not specified                     |

| Capacitance (wire to wire)                 | 30 pF/ft, maximum                 |

| Twist Four per foot                        | 0.33/in, minimum                  |

| EMC                                        | Per MIL-E-6151                    |

#### COMPARISON: MIL-STD-1553 vs. RS-485

Like MIL-STD-1553, RS-485 is based on the use of differential signaling. However, in many respects, RS-485 is a less robust standard than 1553. For example, RS-485's minimum bus voltage is 1.5 volts peak (3.0 volts peak-to-peak), which is half of the MIL-STD-1553 minimum bus voltage of 6.0 volts peak-to-peak. Similarly, in order to provide a degree of noise immunity, 1553 specifies higher voltages for receiver threshold than RS-485, including (in effect), "must reject" voltages.

For rise and fall times, in order to control EMI emissions, MIL-STD-1553 specifies both a minimum and maximum, while 485 specifies only a maximum. In addition, while MIL-STD-1553 provides a clear delineation of bus "dead time", RS-485 does not.

Further, 1553 defines specs in a number of areas for which RS-485 is "silent" about. These include isolation method and options for either direct or transformer coupling; ranges for bus voltages delivered to receivers (loss budget); transmitter limitations and receiver tolerances for zerocrossing distortion (jitter); noise rejection (bit error rate); and terminal input impedance.

Table 2 provides a comprehensivecomparison of MIL-STD-1553's physicallayer relative to RS-485.

## Table 2. Physical Layer Comparison: MIL-STD-1553 vs RS-485

| Characteristic                          | MIL-STD-1553                                                                                                                                                                                        | RS-485                                                                                                                                                  | Advantage/Benefit                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type of Signaling                       | Differential                                                                                                                                                                                        | Differential                                                                                                                                            | Even. Both MIL-STD-1553 and RS-485 use differential signaling.                                                                                                                                                                                                                                                                                                             |

| Signal Encoding Method                  | Manchester Bi-Phase                                                                                                                                                                                 | Not specified.                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                                                                                        |

| Transmit Voltage                        | Direct Coupled: 6.0 to 9.0 $V_{PK-PK}$<br>Transformer Coupled: 18.0 to 27.0 $V_{PK-PK}$                                                                                                             | Differential voltage = 1.5 to 5.0<br>volts = 3.0 to 10.0 V <sub>PK-PK</sub>                                                                             | <b>MIL-STD-1553.</b> For both direct and transformer-coupled configurations, MIL-STD-1553 provides a higher minimum bus voltage: 6.0 $V_{PK-PK}$ direct-coupled, or 6.36 $V_{PK-PK}$ transformer-coupled.                                                                                                                                                                  |

| Rise/Fall Times (10% to 90%)            | 100 to 300 nS                                                                                                                                                                                       | ≤0.3•UI                                                                                                                                                 | MIL-STD-1553. For MIL-STD-1553, a stream of all Manchester "1"s or "0"s results in rise/fall times in the range of 0.2•UI to 0.6•UI. For alternating "1"s and "0"s, the corresponding rise/fall times are 0.1•UI to 0.3•UI. MIL-STD-1553's upper limit is equivalent to that for RS-485. MIL-STD-1553's lower limit of 100 nS serves to minimize EMI and over/undershoots. |

| Transmitter Zero-<br>Crossing Deviation | ≤ ±25 nS                                                                                                                                                                                            | Not specified                                                                                                                                           | <b>MIL-STD-1553.</b> MIL-STD-1553 specifies an upper bound on transmit jitter, thereby providing increased margin for distortion introduced by bus cabling and stubs.                                                                                                                                                                                                      |

| Non-Transmitting Output<br>Noise        | Direct Coupled: ≤ 5 mV RMS<br>line-to-line<br>Transformer Coupled: ≤ 14<br>mV RMS line-to-line                                                                                                      | Defines a maximum offset<br>voltage in the range of -1.0 to<br>+3.0 volts.                                                                              | <b>MIL-STD-1553.</b> MIL-STD-1553's more stringent requirement for non-transmitting output voltage guarantees a lower maximum level of interference from inactive (non-transmitting) nodes.                                                                                                                                                                                |

| Output Symmetry –<br>Residual Voltage   | Direct Coupled: ≤ 90 mV<br>peak, line-to-line Voltage 2.5<br>µS after last mid-bit crossing<br>Transformer Coupled: ≤ 250<br>mV peak, line-to-line Voltage<br>2.5 µS after last mid-bit<br>crossing | Maximum common mode<br>voltage is -3.0 to +1.0 volts.<br>Maximum difference between<br>positive and negative peak<br>voltages must be $\leq$ 0.2 volts. | <b>MIL-STD-1553.</b> MIL-STD-1553's requirement for a maximum residual (or "tailoff") voltage 2.5 $\mu$ S following the end of a transmission ensures non-interference with the subsequent transmission on the bus. In addition, RS-485's allowance for a DC offset voltage complicates the use of transformer isolation.                                                  |

| Node isolation.                         | Isolation transformers are required for all MIL-STD-1553 terminals.                                                                                                                                 | Isolation is not required.                                                                                                                              | <b>MIL-STD-1553.</b> MIL-STD-1553's requirement for transformer isolation ensures a high degree of ground isolation, and lightning and common mode rejection.                                                                                                                                                                                                              |

| Bus-to-Bus Isolation                    | ≥ 45 dB                                                                                                                                                                                             | None                                                                                                                                                    | <b>MIL-STD-1553.</b> MIL-STD-1553 limits crosstalk between redundant buses.                                                                                                                                                                                                                                                                                                |

| Fault Isolation                         | Direct Coupled:<br>55 ohm Series Resistors in<br>Each Terminal Leg                                                                                                                                  | None                                                                                                                                                    | <b>MIL-STD-1553.</b> The requirement for isolation resistors prevents a short-circuited terminal or stub from taking the entire bus out of operation.                                                                                                                                                                                                                      |

| Characteristic                                 | MIL-STD-1553                                                                                                                                                                                        | RS-485                                                                                                                          | Advantage/Benefit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | Transformer Coupled:<br>0.75•Z <sub>0</sub> Series Resistors in<br>Each Stub Leg                                                                                                                    |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bus Coupling<br>Transformer                    | Turns Ratio: 1.4 to 1.0 (step-<br>down, bus to stub)<br>Open Circuit Impedance: ≥<br>3,000 ohms, over 75 KHz to 1<br>MHz<br>Droop: ≤ 20%<br>Ringing: ≤ 1V peak<br>Common Mode Rejection: ≥<br>45 dB | N/A                                                                                                                             | <b>MIL-STD-1553.</b> The option for transformer coupling provides increased stub impedance, matched transmitter impedance, improved ground isolation, and provides a higher degree of lightning immunity.                                                                                                                                                                                                                                                                                            |

| Signal Level Delivered By<br>Bus to Stub       | Direct Coupled: 1.4 to 20 V <sub>PK-PK</sub> , line-to-line<br>Transformer Coupled: 1.0 to<br>14 V <sub>PK-PK</sub> , line-to-line                                                                  | Not specified                                                                                                                   | <b>MIL-STD-1553.</b> MIL-STD-1553A specified a maximum cable distance of 300 feet. While MIL-STD-1553B dropped this requirement, it requires a minimum (and maximum) voltage to be presented to each terminal and/or stub on the bus. This forces implementers to design terminals, buses and stubs in such a way to ensure reliable network operation.                                                                                                                                              |

| Receiver Signal Range                          | Direct Coupled: 1.2 to 20<br>$V_{PK-PK}$ , line-to-line<br>Transformer Coupled: 0.86 to<br>14 $V_{PK-PK}$ , line-to-line                                                                            | -0.2V (peak) ≤ threshold<br>voltage ≤ +0.2V (peak). This<br>implies a receiver "threshold" of<br>0.0 to 0.4 volts peak-to-peak. | <b>MIL-STD-1553.</b> MIL-STD-1553 allows higher receiver thresholds than RS-485, thereby providing a lower bit error rate.<br>Further, MIL-STD-1553 receivers must provide a "dead zone" of                                                                                                                                                                                                                                                                                                          |

| Receiver "No Response"<br>Range                | Direct Coupled: 0 to 0.28 V <sub>PK-</sub><br>PK, line-to-line<br>Transformer Coupled: 0 to<br>0.2 V <sub>PK-PK</sub> , line-to-line                                                                |                                                                                                                                 | 0.28 V $V_{PK-PK}$ = ±0.14 $V_{PK}$ (direct coupled), or 0.2 V $V_{PK-PK}$ = ±0.1 $V_{PK}$ (transformer coupled), thereby providing improved noise immunity. In addition, this improves the capability for a 1553 receiver to be able to determine the end of a received signal transmission. For TTP, this enables shorter gap times between transmissions by individual nodes.<br>RS-485's minimum receiver threshold of 0V can result in receiver output jitter when there is no received signal. |

| Receiver Zero-Crossing<br>Distortion Tolerance | ≥ ±150 nS                                                                                                                                                                                           | Not specified.                                                                                                                  | <b>MIL-STD-1553.</b> This 1553 requirement provides tolerance for phase shifts introduced by transmitters, bus cabling and stubs.                                                                                                                                                                                                                                                                                                                                                                    |

| Receiver Common Mode<br>Rejection              | ± 10 V <sub>PEAK</sub> , line-to-ground,<br>DC to 2 MHz                                                                                                                                             | Receivers must operate over a<br>common mode voltage range of<br>-7V to +12V                                                    | <b>MIL-STD-1553.</b> MIL-STD-1553's common mode range is slightly higher, $\pm 10V_{PK} = 20 V_{PK-PK}$ vs. RS-485's of $\pm 12/-7 V_{PK} = 19 V_{PK-PK}$ .<br>In practice, MIL-STD-1553's requirement for transformer isolation                                                                                                                                                                                                                                                                     |

| Characteristic                       | MIL-STD-1553                                                                                                                                                                                                                                                                                                                   | RS-485                                                                                                                                                                                                                                                                                                                                                                                                                                           | Advantage/Benefit                                                                                                                                                                                                                                            |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | For transformer-coupled<br>stubs, coupling transformers<br>must have a common mode<br>rejection ratio greater than<br>45.0 dB at 1.0 MHz.                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | provides a greater common mode rage than $\pm 10V_{PK}$ . In addition, MIL-STD-1553's option for transformer coupling with a common mode rejection ratio of 45 dB for coupling transformers provides a further improvement in overall common mode rejection. |

| Noise Rejection (Word<br>Error Rate) | Direct Coupled:<br>• $3.0 V_{PK-PK}$ Signal<br>Level<br>• $200 \text{ mV}$ RMS White<br>Gaussian Noise, 1.0<br>to 4.0 MHz<br>• Word Error Rate <<br>10-7<br>Transformer Coupled:<br>• $2.1 V_{PK-PK}$ Signal<br>Level<br>• $140 \text{ mV}$ RMS White<br>Gaussian Noise, 1.0<br>to 4.0 MHz<br>• Word Error Rate <<br>$10^{-7}$ | No specified                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>MIL-STD-1553.</b> MIL-STD-1553's noise rejection (bit error rate) test<br>ensures the implementation of receiver filtering, thereby providing<br>reliable operation in the presence of differential noise.                                                |

| Terminal Input<br>Impedance          | Direct Coupled: ≥ 2,000<br>ohms, over 75 KHz to 1 MHz<br>Transformer Coupled: ≥<br>1,000 ohms, over 75 KHz to 1<br>MHz                                                                                                                                                                                                         | Defines the concept of "unit<br>load", in which a receiver's,<br>transmitter's, or transceiver's<br>DC resistance is approximately<br>8.7 K $\Omega$ to 12 K $\Omega$ . A receiver's,<br>transmitter's, or transceiver's<br>overall input impedance,<br>including reactive (i.e.,<br>capacitive) components, is not<br>specified. In addition, the input<br>resistance can be either less<br>than, equal to, or greater than<br>one "unit load". | <b>MIL-STD-1553.</b> MIL-STD-1553's minimum values for terminal impedance provide a limitation of the bus voltage loading by individual terminals, and minimize distortion resulting from transmission line reflections.                                     |

#### CONCLUSION

Currently, TTP (Time Triggered Protocol) does not specify a physical layer standard. The physical layer defined by MIL-STD-1553 is a strong candidate for use with time triggered networking technologies such as TTP and FlexRay. In particular, MIL-STD-1553 provides higher transmit voltages and receiver thresholds relative to RS-485. In addition, 1553 provides detailed specifications in a number of areas which are not defined by RS-485, including transmitter zero-crossing distortion and receiver zero-crossing tolerance, isolation method, terminal output noise, common mode and noise rejection, and input impedance.

MIL-STD-1553's higher bus voltages and other specs make it highly suitable for use in a passive, multi-drop topology. Use of a passive, multi-drop topology reduces or eliminates the need for active star couplers, thereby leading to reductions in the associated total cable length, cost, power, weight, and volume.

# MIL-STD-1553 Physical Layer (PHY) for TTP – Test Results

## Introduction

Time Triggered Protocol (TTP) is emerging as a strong candidate for use in real-time distributed processing control systems in commercial aircraft. Early implementations of TTP in commercial aircraft have faced challenges meeting the environmental requirements of an aircraft, especially lightning and HIRF. RS-485 has been the de facto physical layer for TTP yet a detailed analysis found RS-485 to be lacking is several key areas. RS-485 suffers from a low transmit signal, low receiver threshold, inadequate isolation method, short stub length and is non-specific in many areas (interoperability issues).(1)

MIL-STD-1553 is a 1 Mbps deterministic serial data bus that has been in use in realtime critical systems in military aircraft for over 30 years. MIL-STD-1553 was designed specifically for use in an aircraft environment and as such provides robust performance in terms of isolation and noise immunity. MIL-STD-1553 is an ideal physical layer for use with TTP.

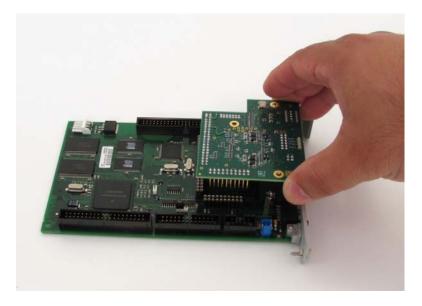

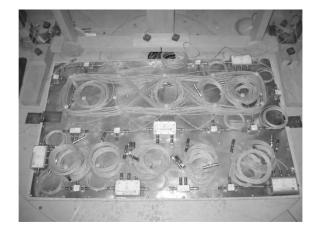

This report summarizes characterization testing that was performed on MIL-STD-1553 as a physical layer for Time Triggered Protocol (TTP). A 1553 physical layer board (1553 PHY) was developed by Data Device Corporation. The 1553 PHY was designed to be installed on a TTP development board (refer to Figure 1).

Figure 1. DDC's 1553 PHY Board for TTTech's Powernode TTP Controller Board

DDC's 1553 PHY board contains two MIL-STD-1553 transmitter/receivers (transceivers). The transceivers on the 1553 PHY board were designed to operate at data rates up to 5 Mbps. The TTP controller on the Powernode boards operates at 4 Mbps.

## **Test Equipment Used**

Tektronix TDS5034B Oscilloscope Tektronix P6246 Differential Probe Tektronix 1103 TekProbe Power Supply HP4396A Network / Spectrum Analyzer HP85016A S-Parameter Test Set Micronetics NOD-5107 Noise Source Lambda LPT-7202-FM Power Supply MIL-STD-1553 cables of various lengths North Hills NH12826 MIL-STD-1553 Bus Couplers North Hills 0101BB Baluns (50 ohm unb to 75 ohm bal) Trompeter TNG-1-78 Terminators (78 ohm) 70 ohm Resistive Load Kay Elemetrics Corp Model 432D Attenuator

## **Transmitter Characteristics**

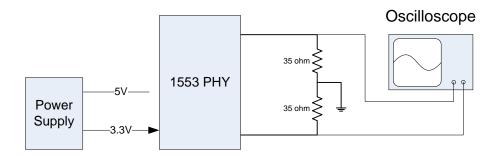

#### Setup

The setup for the 1553 PHY board transmitter measurements is shown in Figure 2. The 1553 PHY board contains DIP switches which can be used to enable test modes of operation. An external power supply was used to supply 5V and 3.3V to the 1553 PHY board. The DIP switches on 1553 PHY board were configured such that the board transmitted a fixed test pattern. The transmit test pattern consisted of a MIL-STD-1553 word that included a Sync plus 17 Manchester encoded bits at a data rate of 5 Mbps with a 25% transmit duty cycle. An oscilloscope was used to measure the output of the transmitter across a resistive load.

Figure 2. Transmitter Test Configuration

#### **Measurements**

#### Amplitude

MIL-STD-1553 specifies amplitude of the transmitter to be in the range of 18 to 27  $V_{PP}$  across a 70 ohm resistive load. The amplitude of the 1553 PHY board was measured differentially across a 70 ohm resistive load. The transmit amplitude was 24 volts peak to peak (within the MIL-STD-1553 specification).

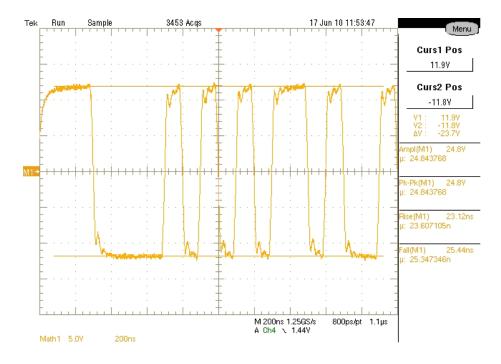

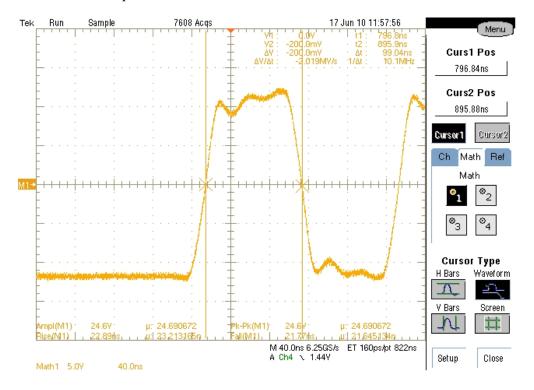

Figure 3. Transmit Waveform Showing Amplitude

### **Risetime/Falltime**

MIL-STD-1553 specifies a transmitter to maintain a rise and fall time within the range of 100 to 300 ns for a 1 Mbps data rate. The 1553 PHY board is designed to run at 5 Mbps so the rise/fall time of the waveform needs to be scaled accordingly (i.e. 20 to 60 ns). The rise and fall time of the 1553 PHY board was measured to be 23 ns (refer to Figure 4).

Figure 4. Transmit Waveform Showing Rise/Fall Time

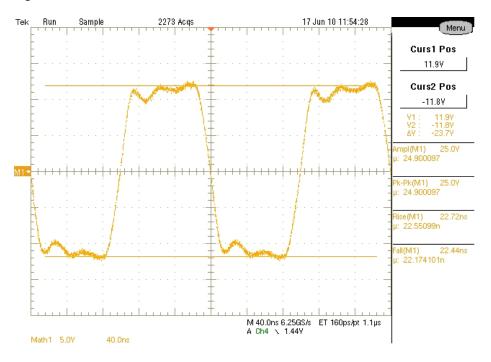

### **Zero Crossing Stability**

A Manchester line code produces a series a pulses in which the zero crossing points will be at multiples of the baud rate (i.e. multiples of 500 ns for 1 Mbps MIL-STD-1553). MIL-STD-1553 specifies that a transmitter must maintain a specific tolerance, referred as zero crossing stability, on the timing between subsequent transitions. The zero crossing tolerance for 1 Mbps MIL-STD-1553 is +/-25 ns (5% of the baud time). The 1553 PHY board is designed to run at a Manchester coded data rate of 5 Mbps, which utilizes a 100 ns baud time. The proposed zero crossing stability for a 5 Mbps data rate is 5% of 100 ns or +/-5 ns. Figure 5 shows the timing between consecutive zero crossings to be 98.96 ns, which is well within the proposed tolerance of 100ns +/-5 ns. Note the zero crossing shown in Figure 5 is the first transition following the 1553 "sync" field. The large difference in frequency content between the sync pulse (consisting of pulse that is 3 baud times wide) and a data bit pulse (1 baud time wide) generally causes a large zero crossing error. In this case the zero crossing stability is well within spec.

Figure 5. Zero Crossing Stability of 5 Mbps Manchester Coded Data

#### Analysis

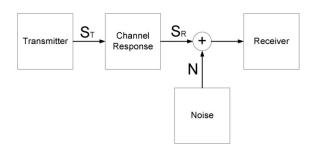

A MIL-STD-1553 data bus will introduce both amplitude and phase distortion. Amplitude distortion will be in the form of attenuation while phase distortion will have the effect of changing the width of the transmitted pulses (i.e. shift the zero crossing points on the waveform). In order to bound the performance of the network it is necessary to specify both the transmitter and receiver with regards to amplitude and phase distortion. They two key transmit characteristics are amplitude and zero crossing tolerance.

## **Receiver Characteristics**

### **Receiver Threshold**

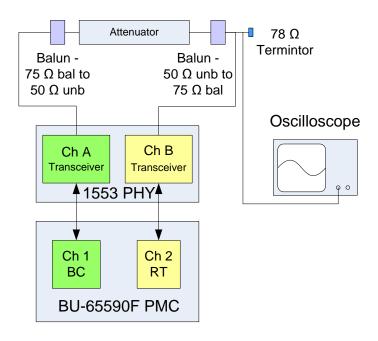

The receiver threshold on the 1553 PHY board was tested by plugging the 1553 PHY board into a test connector on a BU-65590F PMC card. The BU-65590F PMC card was loaded with custom FPGA firmware that would utilize transceivers on the 1553 PHY board and would implement MIL-STD-1553 protocol running at 5 Mbps.

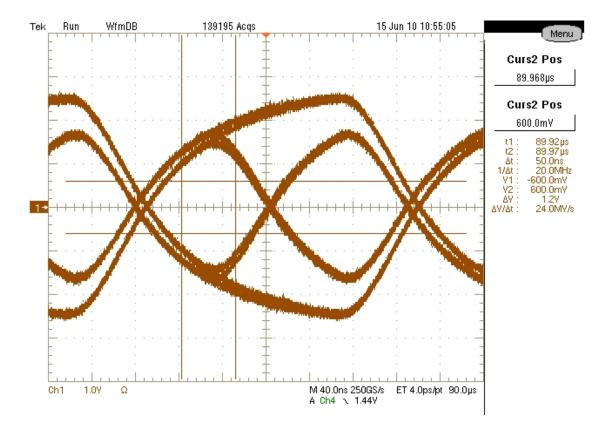

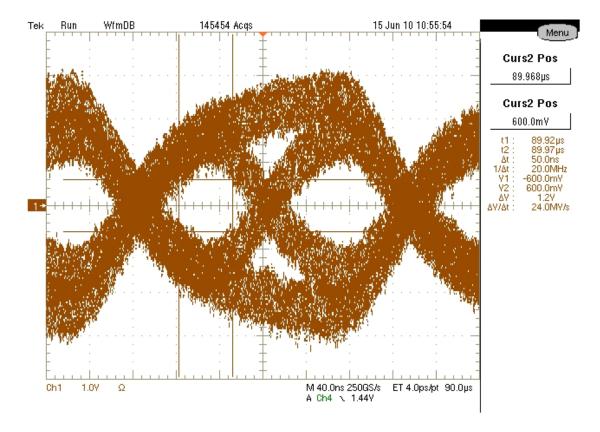

Channel 1 on the BU-65590F PMC card was configured as a 1553 Bus Controller (BC) utilizing transceiver channel A on the 1553 PHY board while channel 2 on the PMC was configured as a Remote Terminal utilizing channel B on the 1553 PHY board. A pair of baluns and a programmable attenuator was used to decrease the amplitude of the BC signal to determine the receiver threshold of the RT (refer to Figure 6).

Figure 6. MIL-STD-1553 Receiver Threshold

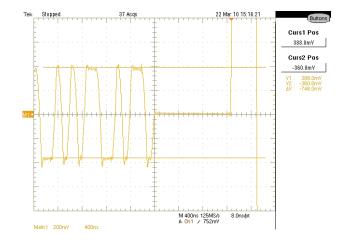

The BU-65590F PMC and 1553 PHY boards were installed in a computer and custom software was written to run the BC and RT while displaying total message count along with an associated error count. The test was started with no attenuation (0 dB). The Bus Controller was setup to continuously send messages. The RT response was observed on the oscilloscope and was confirmed on the computer display (total messages increasing with zero errors). The attenuator was then used to decrease the amplitude of the BC signal until the RT stopped responding and the resulting signal level was measured on the oscilloscope (see Figure 7 for a sample waveform).

Figure 7. Attenuated BC Signal and RT Response

On channel A it was determined that the RT would not respond to a BC signal of 530 mV and would respond to a BC signal of 600 mV. On channel B the no response threshold was also 530 mV while the response threshold was 595 mV.

#### **Receiver Filter Frequency Response**

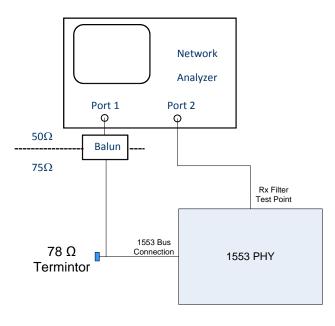

The frequency response of the receiver filter on the 1553 PHY board was characterized using an HP4396A Network Analyzer with an HP85016A S-Parameter Test Set (refer to Figure 8). A balun was connected to port 1 on the network analyzer. The purpose of the balun was to convert the unbalanced output from the network analyzer to a balanced signal and to convert the impedance from 50 ohms to 75 ohms. Port 2 on the network analyzer was connected to a receiver test point on the 1553 PHY board (i.e. the output of the receiver filter).

Figure 8. Receiver Filter Frequency Response Measurement

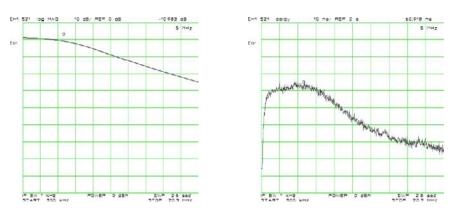

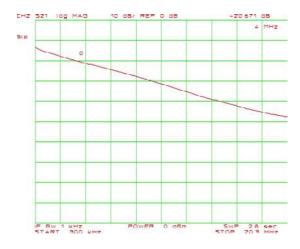

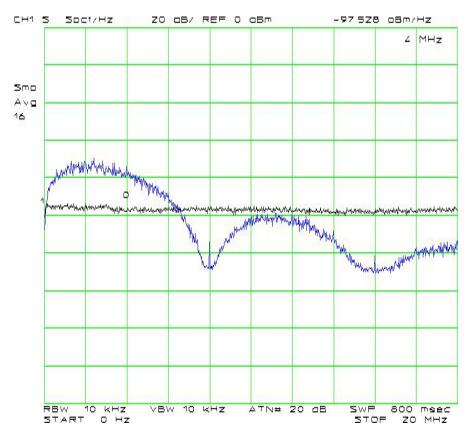

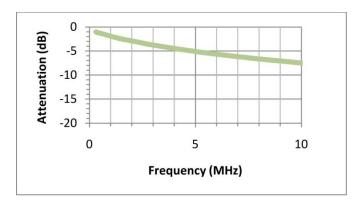

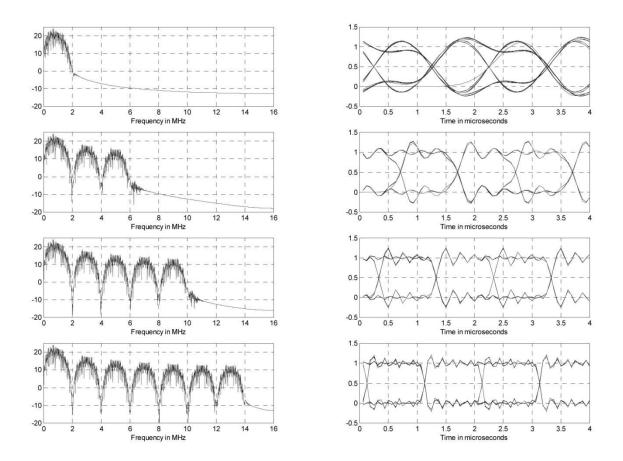

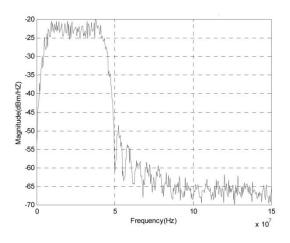

The network analyzer was programmed for a sweep frequency from 300 KHz to 20.3 MHz. The magnitude and group delay for the S21 (forward gain) are shown in Figure 9.

Figure 9. Gain Magnitude and Group Delay of Receiver Filter

### **Receiver Zero Crossing Distortion**

A Manchester coded signal will consist of consecutive pulses with a width equal to the baud rate (500 ns for 1 Mbps 1553 and 100 ns for a 5 Mbps data rate). Phase distortion in the channel (i.e. on the bus) will have the effect of increasing or decreasing the width of each pulse (i.e. shifting the zero crossing point between consecutive transitions). The receiver needs to be designed to tolerate this phase distortion. MIL-STD-1553 specifies that a receiver must be able to decode a waveform with a zero crossing error of up to 150 ns (30% of the baud time) for a 1 Mbps data rate. The proposed limit for a 5 Mbps rate is 30% of 100 ns or 30 ns.

The zero crossing performance of a receiver is dependent on the combination of the analog receiver and the digital decoder. The analog receiver will convert the received signal into a series of digital pulses. The decoder will recover the embedded clock and convert the digital pulse stream into a serial data stream. The 1553 PHY board implements the analog receiver function while the TTP controller on the Powernode implements the decoder function.

Testing the receiver zero crossing distortion of a receiver requires specialized test equipment. For MIL-STD-1553 companies such as DDC provide MIL-STD-1553 test equipment that has the ability to transmit signals to a receiver under test with a programmable zero crossing error. It is our understanding that this type of equipment does not exist for TTP. TTP is also a more complicated protocol so it appears that a simple pattern generator cannot be used to test the receiver. A true test of the receiver will require a specialized tester that implements the TTP protocol.

The receiver filter characterization in the Receiver Filter Frequency Response section shows that the amplitude and group delay of the 1553 receiver is consistent over the proposed pass band, which implies that the receiver will not induce additional amplitude and phase distortion and thus the performance of the receiver in terms of tolerance to zero crossing distortion will be determined primarily by the digital decoder within the TTP controller. A more detailed understanding of the operation of the TTP controller will be required to assess the zero crossing performance of the decoder.

## Analysis

The receiver threshold of the 1553 PHY is consistent with the values defined in MIL-STD-1553, thus the loss budget between a transmitted and received signal will be similar to that of MIL-STD-1553 (amplitude distortion). Although the receiver zero crossing distortion was not tested it is believed that the performance should be similar to 1 Mbps 1553. The analog receiver was shown to maintain the amplitude and phase of the received signal and the same decoder algorithm used in MIL-STD-1553 could be used with TTP (assuming that the decoder in the TTP controller is found to be deficient).

# **Network Characteristics**

# Setup

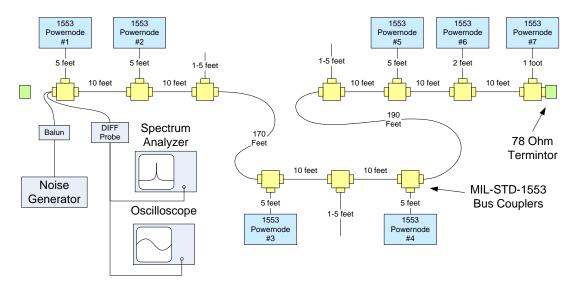

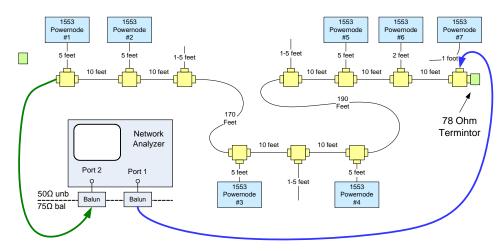

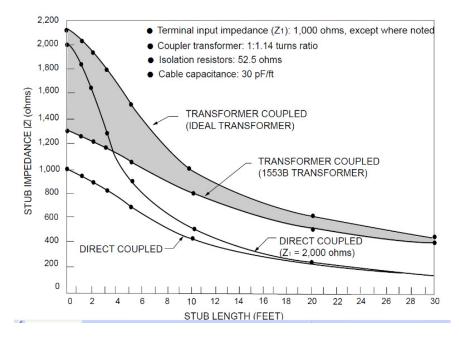

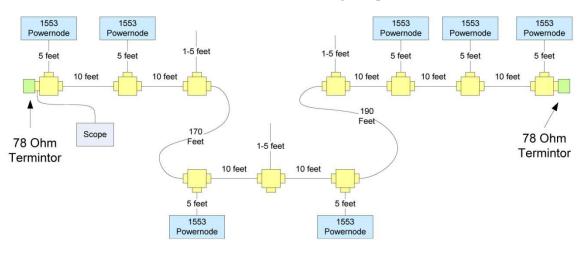

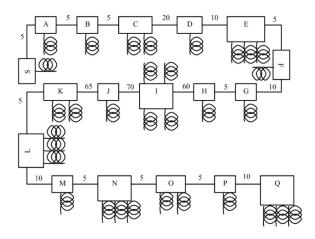

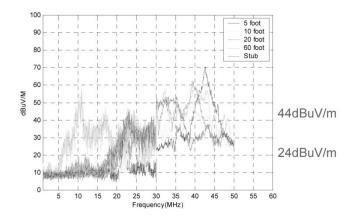

A test network was assembled consisting of a main bus length of 430 feet with 10 stub connections (refer to Figure 10). Each stub connection utilizes a standard MIL-STD-1553 bus coupler consisting of a coupling transformer and a pair of isolation resistors (as defined in MIL-STD-1553). Powernode cards with 1553 PHY boards installed on them (referred to as 1553 Powernodes) were connected to seven of the stubs on the bus. The other 3 stubs were terminated in a simulated load of 2000 ohms.

#### Figure 10. 430 Foot Test Bus

The terminator on one end of the bus (near 1553 Powernode #1) was removed and the end of the bus was connected to an NOD-5107 noise generator for bit error rate testing. A balun was used to convert the 50 ohm unbalanced output impedance of the noise generator to a 75 ohm balanced impedance (to match the 78 ohm impedance of the 1553 bus). The NOD-5107 outputs random noise from 100 Hz to 100 MHz with a maximum output power of -70 dBm/Hz.

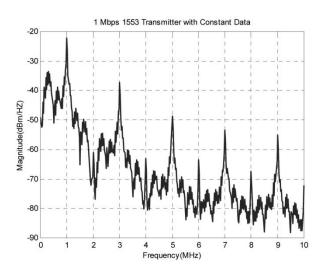

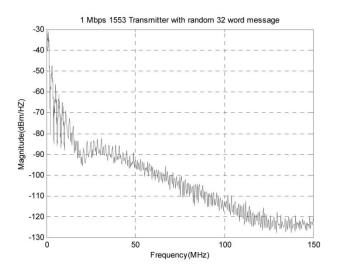

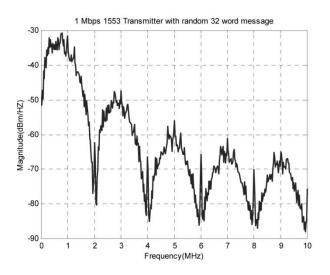

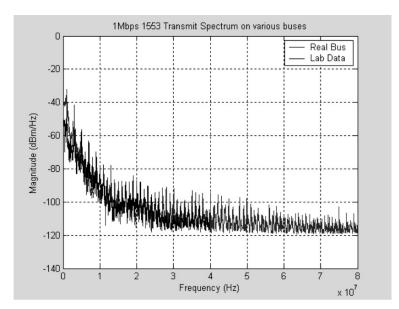

Each 1553 Powernode contains custom firmware that implements a cluster cycle consisting of 2 rounds with a 4 ms cycle time. Each 1553 Powernode will send a 240 byte X-Frame in each of the two rounds (each X-Frame contains 16 bytes of TTP status